# Section I. Arria GX Transceiver User Guide

This section provides information on the configuration modes for  $Arria^{TM}$  GX devices. It also includes information on testing, Arria GX port and parameter information, and pin constraint information.

This section includes the following chapters:

- Chapter 1, Arria GX Transceiver Architecture

- Chapter 2, Arria GX Transceiver Protocol Support and Additional Features

- Chapter 3, Arria GX ALT2GXB Megafunction User Guide

- Chapter 4, Specifications and Additional Information

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the full handbook.

Altera Corporation Section I–1

Section I–2 Altera Corporation

# 1. Arria GX Transceiver Architecture

AGX52001-1.2

# Introduction

The Arria<sup>TM</sup> GX is a protocol-optimized FPGA family that leverages Altera<sup>®</sup>'s advanced multi-gigabit transceivers. The Arria GX transceiver blocks build on the success of the Stratix<sup>®</sup> II GX family and are optimally designed to support the following serial connectivity protocols (functional modes):

- PCI Express (PIPE)

- Gigabit Ethernet (GIGE)

- Serial RapidIO

# **Building Blocks**

Arria GX transceivers are structured into full duplex (transmitter and receiver) four-channel groups called transceiver blocks. The Arria GX device family offers up to 12 transceiver channels (three transceiver blocks) per device. You can configure each transceiver block to one of the three supported functional modes; for example, four GIGE ports or one four-lane (×4) PCI Express (PIPE) port. In Arria GX devices that offer more than one transceiver block, you can configure each transceiver block to a different functional mode; for example, one transceiver block configured as a four-lane (×4) PCI Express (PIPE) port and the other transceiver block can be configured as four GIGE ports.

In addition to providing the physical coding sublayer (PCS) and physical media attachment (PMA) circuitry for each functional mode, Arria GX transceivers support the following protocol specific features:

- PCI Express (PIPE)

- 2.5 Gbps (PCI Express Generation 1) line rate

- ×1 (Individual single-lane) and ×4 (Bonded four-lane) link widths

- Synchronous PCI Express (rate matching FIFO bypass capability)

- PCI Express synchronization state machine

- Receiver detection

- Electrical Idle generation/detection

- Polarity inversion

- Power state management

#### GIGI

- 1.25 Gbps line rate

- Synchronization state machine

- Idle sequence (/I1/, /I2/) generation

- Serial RapidIO

- 1.25 Gbps and 2.5 Gbps line rate

- Synchronization state machine

For a complete set of features supported in each protocol, refer to the *Arria GX Transceiver Protocol Support and Additional Features* chapter in volume 2 of the *Arria GX Device Handbook*.

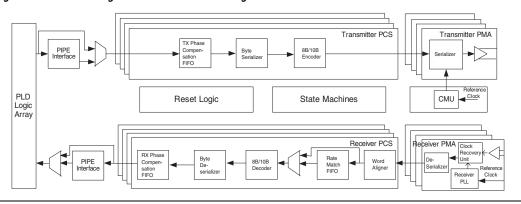

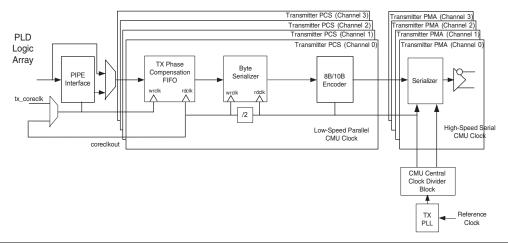

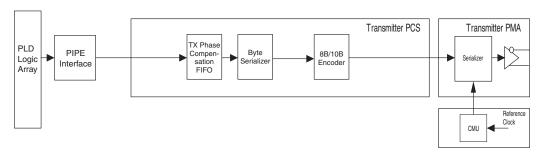

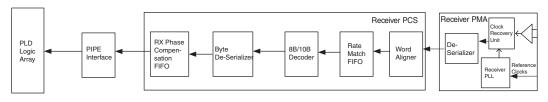

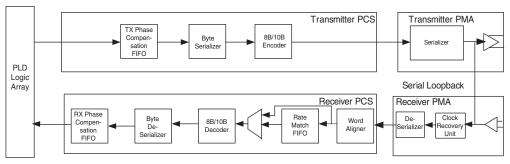

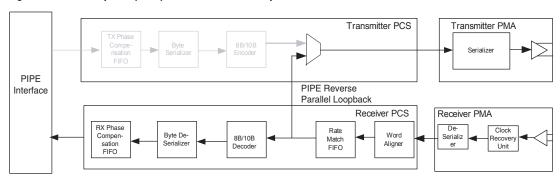

Figure 1–1 shows the Arria GX transceiver block diagram divided into Transmitter and Receiver Digital Circuits (PCS) and Analog Circuits (PMA).

Figure 1-1. Arria GX Gigabit Transceiver Block Diagram

# **Port List**

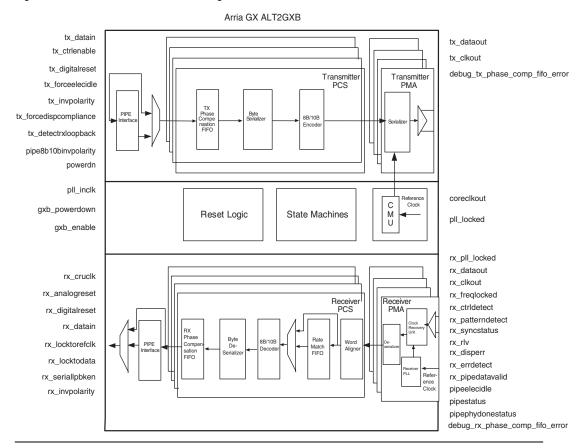

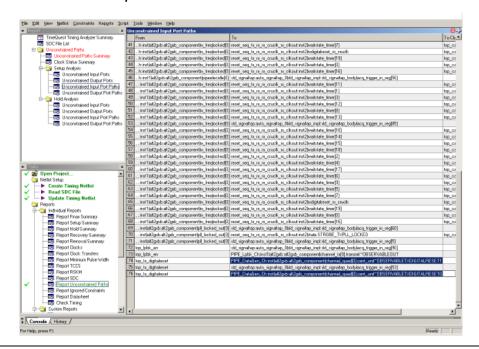

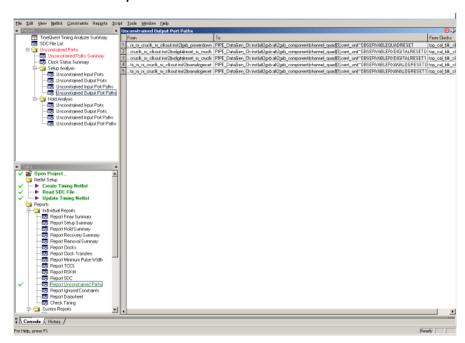

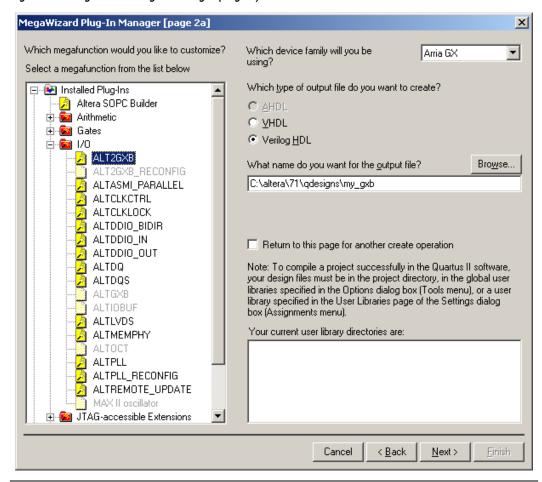

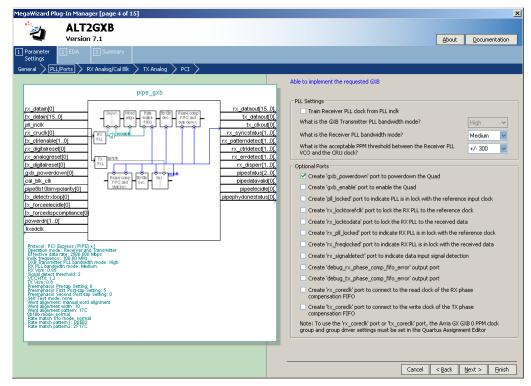

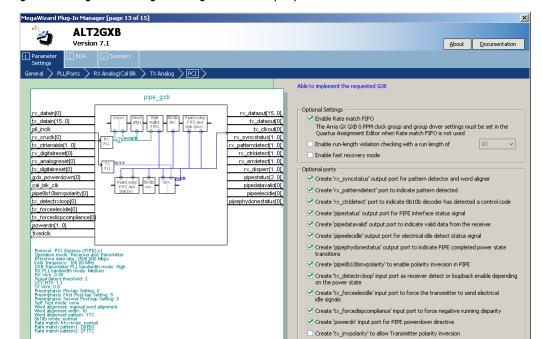

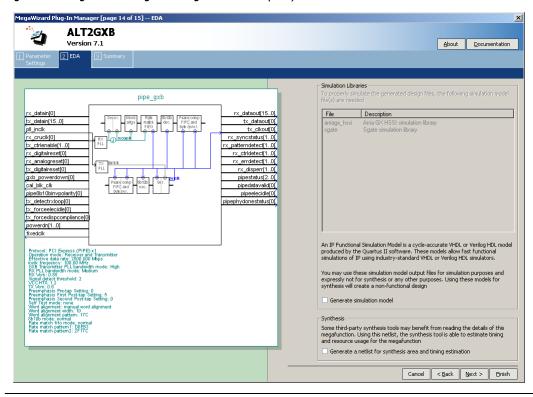

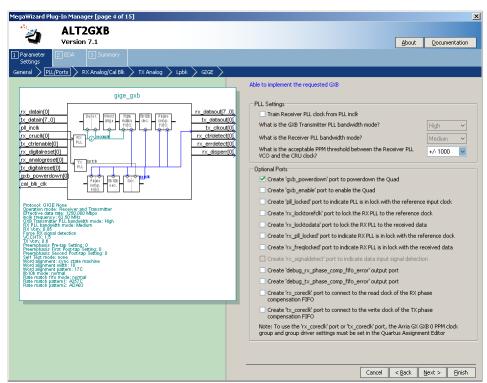

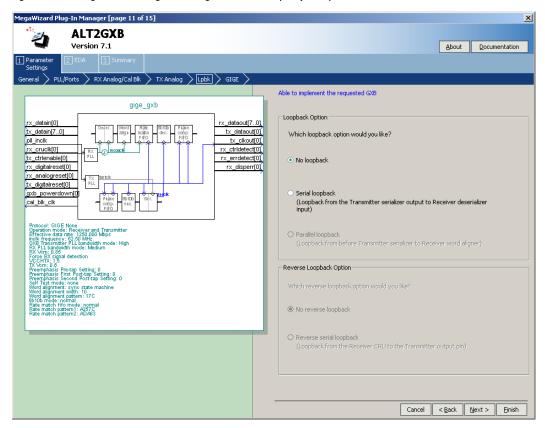

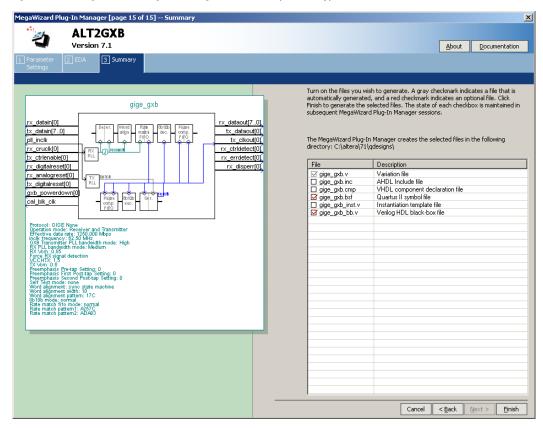

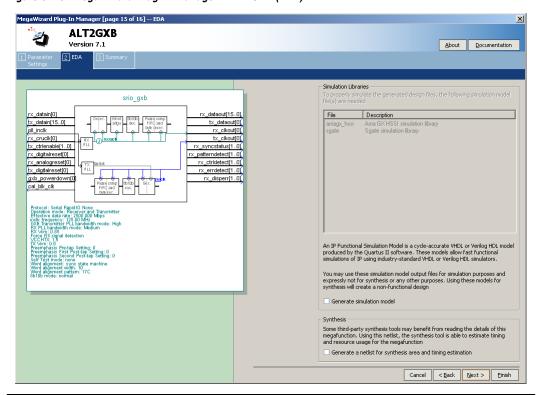

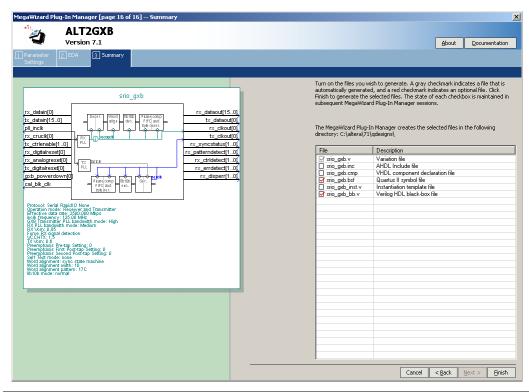

You instantiate the Arria GX transceivers using the ALT2GXB megacore instance provided in the Quartus® II MegaWizard® Plug-In Manager. The ALT2GXB instance allows you to configure the transceivers for your intended protocol and select optional control and status ports to and from the instantiated transceiver channels.

Figure 1–2 shows the port diagram of all available ports in an ALT2GXB transceiver instance.

Figure 1-2. Arria GX Transceiver Port Diagram

Table 1–1 provides a brief description for all available ALT2GXB ports shown in Figure 1-2.

| Port Name                    | Input/Output                                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                      | Scope   |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Receiver Physical Coding Sub | layer (PCS) Ports                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                  |         |

| rx_dataout                   | Output Receiver parallel data output. The bus width depends on the channel width for the selected functional mode multiplied by the number of channels per instance. |                                                                                                                                                                                                                                                                                                                                                                                  |         |

| rx_clkout                    | Output                                                                                                                                                               | Recovered clock from the receiver channel.                                                                                                                                                                                                                                                                                                                                       | Channel |

| rx_coreclk                   | Input                                                                                                                                                                | Optional read clock port for the receiver phase compensation FIFO. If not selected, Quartus II automatically selects rx_clkout/tx_clkout/coreclkout as the read clock for receiver phase compensation FIFO. If selected, you must drive this port with a clock that is frequency locked to rx_clkout/tx_clkout/coreclkout                                                        | Channel |

| rx_rlv                       | Output                                                                                                                                                               | Run-length violation indicator. A high signal is driven when the run length (consecutive '1's or '0's) of the received data exceeds the configured limit.                                                                                                                                                                                                                        |         |

| pipe8b10binvpolarity         | Input                                                                                                                                                                | PCI Express (PIPE) polarity inversion at the 8B/10B decoder input. This port inverts the data at the input of the 8B/10B decoder.                                                                                                                                                                                                                                                | Channel |

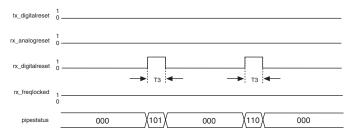

| pipestatus                   | Output                                                                                                                                                               | PCI Express (PIPE) receiver status port. In the case of multiple status signals, the lower number signal takes precedence.  000 – Received data OK  001 – 1 skip added (not supported)  010 – 1 skip removed (not supported)  011 – Receiver detected  100 – 8B/10B decoder error  101 – Elastic buffer overflow  110 – Elastic buffer underflow  111 – Received disparity error | Channel |

| pipephydonestatus            | Output                                                                                                                                                               | Indicates a mode transition completion in PCI Express (PIPE) mode. On completion of a power state transition or receiver detection, a pulse is driven on this port.                                                                                                                                                                                                              | Channel |

| rx_pipedatavalid             | Output                                                                                                                                                               | PCI Express (PIPE) valid data indicator on the rx_dataout port.                                                                                                                                                                                                                                                                                                                  | Channel |

| pipeelecidle                 | Output                                                                                                                                                               | PCI Express (PIPE) signal detect.                                                                                                                                                                                                                                                                                                                                                | Channel |

| Port Name Input/Output Description |             | Description                                                                                                                                                                                                                                     | Scope   |

|------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| rx_digitalreset                    | Input       | Reset port for the receiver PCS block. This port resets all the digital logic in the receiver channel. The minimum pulse width is two parallel clock cycles.                                                                                    | Channel |

| rx_ctrldetect                      | Output      | Receiver control code group indicator port. Indicates whether the data at the output of rx_dataout is a control or data word.                                                                                                                   | Channel |

| rx_errdetect                       | Output      | 8B/10B code group violation signal. Indicates that the data at the output of rx_dataout has a code group violation or a disparity error. Used with disparity error signal to differentiate between a code group error and/or a disparity error. | Channel |

| rx_syncstatus                      | Output      | Indicates the lane synchronization status in all functional modes. A HIGH signal is driven continuously when the synchronization state machine for the selected functional mode detects that all lane synchronization conditions are satisfied. | Channel |

| rx_disperr                         | Output      | 8B/10B disparity error indicator port. Indicates that the data at the output of rx_dataout has a disparity error.                                                                                                                               |         |

| rx_patterndetect                   | Output      | Indicates when the word aligner detects the alignment pattern in the current word boundary.                                                                                                                                                     | Channel |

| rx_invpolarity                     | Input       | Inverts the polarity of the received data at the input of the word aligner                                                                                                                                                                      |         |

| debug_rx_phase_comp_<br>fifo_error | Output      | Indicates receiver phase compensation FIFO overrun or underrun situation                                                                                                                                                                        | Channel |

| Receiver Physical Media Attac      | hment (PMA) |                                                                                                                                                                                                                                                 |         |

| rx_pll_locked                      | Output      | Receiver PLL locked signal. Indicates if the receiver PLL is phase locked to the CRU reference clock.                                                                                                                                           |         |

| rx_analogreset                     | Input       | Receiver analog reset. Resets all analog circuits in the receiver PMA.                                                                                                                                                                          |         |

| rx_freqlocked                      | Output      | CRU mode indicator port. Indicates if the CRU is locked to data mode or locked to the reference clock mode.  0 – Receiver CRU is in lock-to-reference clock mode  1 – Receiver CRU is in lock-to-data mode                                      | Channel |

| Port Name       | Input/Output | Description                                                                                                                                                                                                                                                                                                    | Scope                |

|-----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| rx_signaldetect | Output       | Signal detect port. In PCI Express (PIPE) mode, indicates if a signal that meets the specified range is present at the input of the receiver buffer. In all other modes, rx_signaldetect is forced high and must not be used as an indication of a valid signal at receiver input.                             | Channel              |

| rx_seriallpbken | Input        | Serial loopback control port.  0 – normal data path, no serial loopback  1 – serial loopback                                                                                                                                                                                                                   | Channel              |

| rx_locktodata   | Input        | Lock-to-data control for the CRU. Use with rx_locktorefclk.                                                                                                                                                                                                                                                    | Channel              |

| rx_locktorefclk | Input        | Lock-to-reference lock mode for the CRU. Use with rx_locktodata. rx_locktodata/rx_locktorefclk 0/0 - CRU is in automatic mode 0/1 - CRU is in lock-to-reference clock 1/0 - CRU is in lock-to-data mode 1/1 - CRU is in lock-to-data mode                                                                      | Channel              |

| rx_cruclk       | Input        | Receiver PLL/CRU reference clock.                                                                                                                                                                                                                                                                              | Channel              |

| Transmitter PCS | •            |                                                                                                                                                                                                                                                                                                                | •                    |

| tx_datain       | Input        | Transmitter parallel data input. The bus width depends on the channel width for the selected functional mode multiplied by the number of channels per instance.                                                                                                                                                | Channel              |

| tx_clkout       | Output       | PLD logic array clock from the transceiver to the PLD. In an individual-channel mode (for example, GIGE, PCI Express [PIPE] ×1), there is one tx_clkout per channel.                                                                                                                                           | Channel              |

| coreclkout      | Output       | PLD logic array clock from the transceiver block to the PLD. In bonded-channel mode (x4 PCI Express [PIPE]), there is one coreclkout per transceiver block.                                                                                                                                                    | Transceiver<br>block |

| tx_coreclk      | Input        | Optional write clock port for the transmitter phase compensation FIFO. If not selected, Quartus II automatically selects tx_clkout/coreclkout as the write clock for transmitter phase compensation FIFO. If selected, you must drive this port with a clock that is frequency locked to tx_clkout/coreclkout. | Channel              |

| Port Name                          | Input/Output | Description                                                                                                                                                                                                                                                                                                                           | Scope   |

|------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| tx_detectrxloopback                | Input        | PCI Express (PIPE) receiver detect / loopback pin. Depending on the power state (P0 or P1), the signal either activates receiver detect or loopback.                                                                                                                                                                                  | Channel |

| tx_forceelecidle                   | Input        | PCI Express (PIPE) Force Electrical Idle.<br>When asserted, it tristates the transmitter<br>buffer in PCI Express (PIPE) mode.                                                                                                                                                                                                        | Channel |

| tx_forcedispcompliance             | Input        | PCI Express (PIPE) force negative disparity for compliance pattern. The compliance pattern requires beginning with a negative disparity. Assertion of this port while transmitting the first byte ensures that the first byte is encoded with a negative disparity. This port must be de-asserted after the first byte.               | Channel |

| powerdn                            | Input        | PCI Express (PIPE) power mode port. This port sets the power mode of the associated PCI Express channel. The power modes are as follows: 2'b00: P0 – Normal operation 2'b01: P0s – Low recover time latency, power saving state 2'b10: P1 – Longer recovery time (64us max) latency, lower power state 2'b11: P2 – Lowest power state | Channel |

| tx_digitalreset                    | Input        | Reset port for the transmitter PCS block. This port resets all the digital logic in the transmit channel. The minimum pulse width is two parallel clock cycles.                                                                                                                                                                       | Channel |

| tx_ctrlenable                      | Input        | Transmitter control code group indicator port. Indicates whether the data at the tx_datain port is a control or data word. When high, the 8-bit character is encoded as data code group (Dx.y). When low, the 8-bit character is encoded as control code group (Kx.y)                                                                 | Channel |

| tx_invpolarity                     | Input        | Inverts the polarity of the data to be transmitted at the transmitter PCS-PMA interface (input to the serializer).                                                                                                                                                                                                                    | Channel |

| debug_tx_phase_comp_<br>fifo_error | Output       | Indicates transmitter phase compensation FIFO overrun or underrun situation.                                                                                                                                                                                                                                                          | Channel |

| Transmitter PMA                    |              |                                                                                                                                                                                                                                                                                                                                       |         |

| fixedclk                           | Input        | 125-MHz clock for receiver detect circuitry in PCI Express (PIPE) mode.                                                                                                                                                                                                                                                               | Channel |

| Port Name                      | Input/Output | Description                                                                                                                                                                                                                      | Scope                |

|--------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| CMU PMA                        | •            |                                                                                                                                                                                                                                  | •                    |

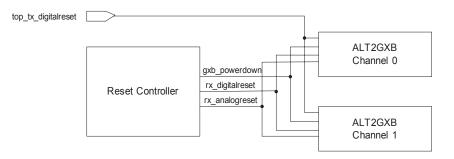

| gxb_powerdown                  | Input        | Transceiver block reset and power down. This resets and powers down all circuits in the transceiver block. It does not power down the REFCLK buffers and reference clock lines.                                                  | Transceiver<br>block |

| gxb_enable                     | Input        | Dedicated transceiver block enable pin. If instantiated, this port must be tied to the dedicated gigabit transceiver block enable input pin.                                                                                     | Transceiver<br>block |

| pll_locked                     | Output       | PLL locked indicator for the transmitter PLLs.                                                                                                                                                                                   | Transceiver block    |

| pll_inclk                      | Input        | Reference clocks for the transmitter PLLs.                                                                                                                                                                                       | Transceiver block    |

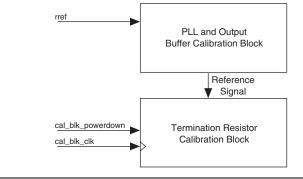

| Calibration Block              |              |                                                                                                                                                                                                                                  |                      |

| cal_blk_clk                    | Input        | Calibration clock for the transceiver termination blocks. This clock supports frequencies from 10 MHz to 125 MHz.                                                                                                                | Device               |

| cal_blk_powerdown (active low) | Input        | Power-down signal for the calibration block. Assertion of this signal may interrupt data transmission and reception. Use this signal to re-calibrate the termination resistors if temperature and/or voltage changes warrant it. | Device               |

| External Signals               |              |                                                                                                                                                                                                                                  |                      |

| tx_dataout                     | Output       | Transmitter serial output port.                                                                                                                                                                                                  | Channel              |

| rx_datain                      | Input        | Receiver serial input port.                                                                                                                                                                                                      | Channel              |

| rrefb (1)                      | Output       | Reference resistor port. This port is always used and must be tied to a 2K-Ω resistor to ground. This port is highly sensitive to noise. There must be no noise coupled to this port.                                            |                      |

| refclk (1)                     | Input        | Dedicated reference clock inputs (two per transceiver block) for the transceiver. The buffer circuitry is similar to the receiver buffer, but the termination is not calibrated.                                                 | Transceiver<br>block |

### Note to Table 1–1:

$(1) \quad \text{These are dedicated pins for the transceiver and do not appear in the MegaWizard Plug-In Manager.}$

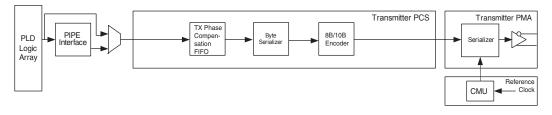

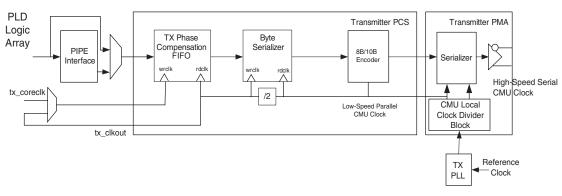

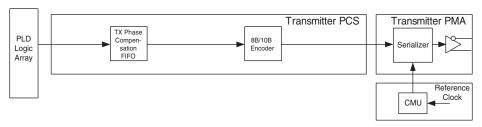

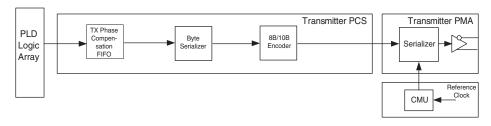

# Transmitter Channel Architecture

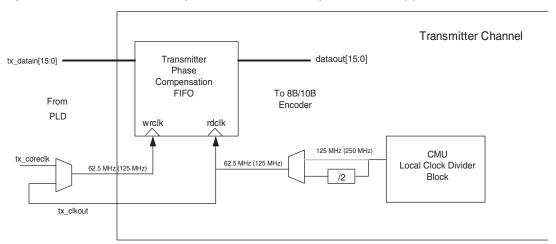

This section provides a brief description about sub-blocks within the transmitter channel (Figure 1–3). The sub-blocks are described in order from the PLD-transmitter parallel interface to the serial transmitter buffer.

Figure 1-3. Arria GX Transmitter Channel Block Diagram

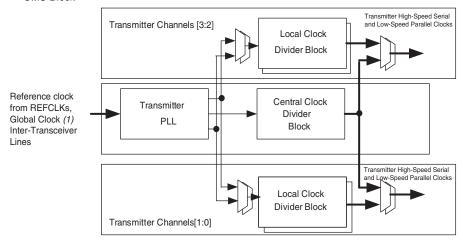

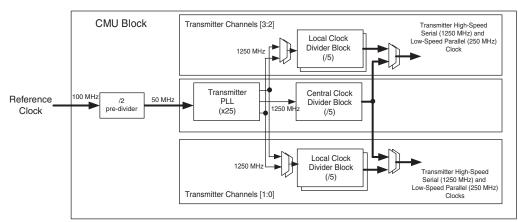

# **Clock Multiplier Unit**

Each transceiver block has a clock multiplier unit (CMU) that takes in a reference clock and synthesizes two clocks: a high-speed serial clock to serialize the data and a low-speed parallel clock used to clock the transmitter digital logic (PCS) and the PLD-transceiver interface.

The CMU is further divided into three sub-blocks

- Transmitter PLL

- Central clock divider block

- Local clock divider block

Each transceiver block has one transmitter PLL, one central clock divider and four local clock dividers. One local clock divider is located in each transmitter channel of the transceiver block.

Figure 1–4 shows a block diagram of the CMU block within each transceiver block.

Figure 1–4. Clock Multiplier Unit Block Diagram

CMU Block

*Note to Figure 1–4:*

(1) The global clock line must be driven from an input pin only.

#### Transmitter PLL

The transmitter PLL multiplies the input reference clock to generate the high-speed serial clock required to support the intended protocol. It synthesizes a half-rate high-speed serial clock that runs at half the frequency of the serial data rate for which it is configured; for example, the transmitter PLL runs at 625 MHz when configured in 1.25 Gbps GIGE functional mode.

The transmitter PLL output feeds the central clock divider block and the local clock divider blocks. These clock divider blocks divide the high-speed serial clock to generate the low-speed parallel clock for the transceiver PCS logic and the PLD-transceiver interface clock. Depending on the functional mode for which the transceiver block is configured, either the central clock divider block or the local clock divider block is used to generate the low-speed parallel clock.

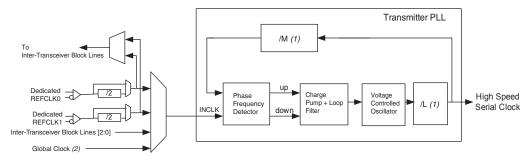

Figure 1–5 shows a block diagram of the transmitter PLL.

Figure 1-5. Transmitter PLL

#### Notes to Figure 1-5:

- (1) You only need to select the protocol and the available input reference clock frequency in the Quartus II MegaWizard Plug-In Manager. Based on your selections, the Plug-In Manager automatically selects the necessary /M and /L dividers (clock multiplication factors).

- (2) The global clock line must be driven from an input pin only.

The reference clock input to the transmitter PLL can be derived from:

- One of the two available dedicated reference clock input pins (REFCLK0 or REFCLK1) of the associated transceiver block

- PLD global clock network (must be driven directly from an input clock pin and cannot be driven by user logic or enhanced PLL)

- Inter-transceiver block lines driven by reference clock input pins of other transceiver blocks

Altera recommends using the dedicated reference clock input pins (REFCLK0 or REFCLK1) to provide the reference clock for the transmitter PLL.

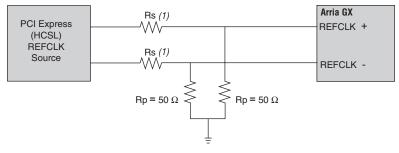

#### **Dedicated Reference Clock Input Pins**

Each transceiver block has two dedicated reference clock input pins (REFCLK0 and REFCLK1). The clock route from REFCLK0 and REFCLK1 pins in each transceiver block has an optional pre-divider that divides the reference clock by two before feeding it to the transmitter PLL (Figure 1–5).

The Quartus II software automatically selects the divide-by-two pre-divider for the reference clock input in PCI Express (PIPE) mode only. In GIGE and Serial Rapid IO modes, the pre-divider is not used.

#### Reference Clock From PLD Global Clock Network

You can drive the reference clock to the transmitter PLL from a PLD global clock network. If you choose this option, you must drive the global PLD reference clock line from a non-REFCLK FPGA input pin. You cannot use a clock generated by PLD logic or an enhanced PLL to drive the reference clock input to the transmitter PLL.

The Quartus II software requires the following setting for the non-REFCLK FPGA input pin used to drive the reference clock input:

Assignment name: Stratix II GX/Arria GX REFCLK coupling and termination setting

Value: Use as regular IO.

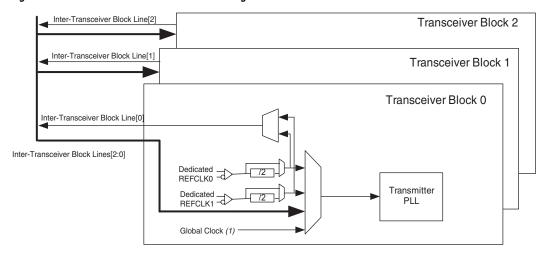

### **Inter-Transceiver Block Line Routing**

The inter-transceiver block lines allow the dedicated reference clock input pins of one transceiver block to drive the transmitter and receiver PLL of other transceiver blocks. There are a maximum of three inter-transceiver block routing lines available in the Arria GX device family. Each transceiver block can drive one inter-transceiver block line from either one of its associated reference clock pins. The inter-transceiver block lines can drive any or all of the transmitter and receiver PLLs in the device. The inter-transceiver block lines offer flexibility when multiple channels in separate transceiver blocks share a common reference clock frequency.

The inter-transceiver block lines also drive the reference clock from the REFCLK pins into the PLD fabric, which reduces the need to drive multiple clocks of the same frequency into the device. If a divide-by-two reference clock pre-divider is used, the inter-transceiver block line driven by the corresponding REFCLK pin cannot be used to clock PLD logic.

The Quartus II software automatically uses the appropriate inter-transceiver line if the transceiver block is being clocked by the dedicated reference clock (REFCLK) pin of another transceiver block.

Figure 1–6 shows the inter-transceiver block line interface to the transceivers in the gigabit transceiver blocks and to the PLD.

Figure 1-6. Inter-Transceiver Block Line Routing

*Note to Figure 1–6:*

(1) The global clock line must be driven from and input pin only.

Depending on the functional mode, the Quartus II software automatically selects the appropriate transmitter PLL bandwidth.

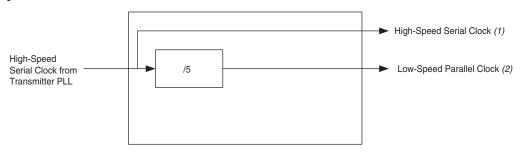

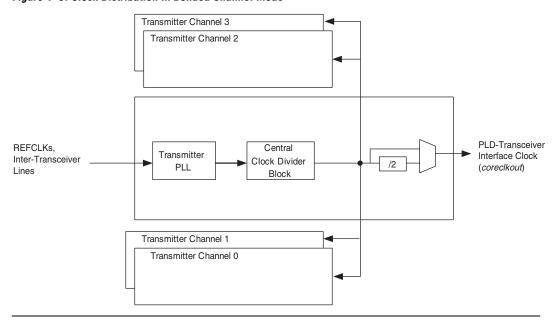

#### Central Clock Divider Block

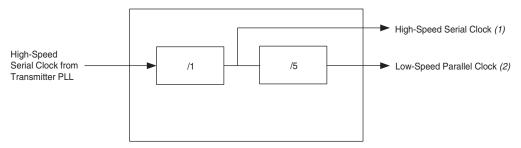

One central clock divider block is available per transceiver block. It takes in the high-speed transmitter PLL clock and divides it to generate the low-speed parallel clock for transceiver PCS logic in ×4 PCI Express (PIPE) bonded-channel mode. The Quartus II software automatically selects /5 as the division factor for all supported functional modes. The central clock divider block also forwards the high-speed serial clock from the transmitter PLL to the serializer, as shown in Figure 1–7.

Figure 1-7. Central Clock Divider Block

#### *Notes to Figure 1–7:*

- (1) High-speed serial clock from the central clock divider block feeds the serializer in all channels within a transceiver block in bonded-channel mode (×4 PCI Express [PIPE]).

- (2) Low-speed parallel clock from the central clock divider block feeds the transceiver PCS logic in all channels within a transceiver block in bonded-channel mode (x4 PCI Express [PIPE]).

The central clock divider block feeds the high-speed and low-speed clock to all the channels in the transceiver block, as shown in Figure 1–8. This ensures that the serializer in each channel outputs the same bit number at any time to minimize the channel-to-channel skew.

Figure 1-8. Clock Distribution in Bonded Channel Mode

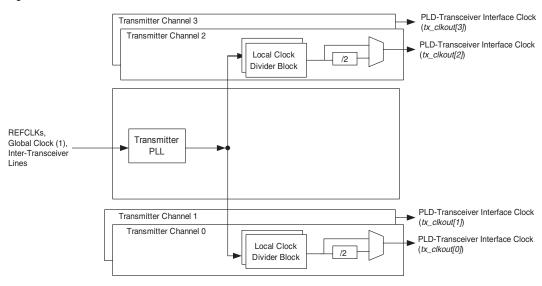

#### Local Clock Divider Block

A local clock divider block is located in each of the four transmitter channels of a transceiver block. It takes in the high-speed transmitter PLL clock and divides it to generate the low-speed parallel clock for transceiver PCS logic in individual channel modes; for example, GIGE mode. The Quartus II software automatically selects /5 as the division factor for all supported functional modes. The local clock dividers also forward the high-speed serial clock from the transmitter PLL to the serializer as shown in Figure 1–9.

Figure 1–9. Local Clock Divider Block Note (3)

#### *Notes to Figure 1–9:*

- High-speed serial clock from the local clock divider block feeds the serializer in its associated channel in individual-channel modes (for example, GIGE).

- (2) Low-speed parallel clock from the local clock divider block feeds the transceiver PCS logic in its associated channel in individual-channel mode (for example, GIGE).

- (3) Each channel within a transceiver block is fed by its own local clock divider block, as shown in Figure 1–10.

Figure 1–10 shows the clock distribution in individual channel mode.

*Note to Figure 1–10:*

(1) The global clock line must be driven from an input pin only.

Figure 1–10. Clock Distribution in Individual Channel Mode

# **Transmitter Phase Compensation FIFO**

A transmitter phase compensation FIFO (Figure 1–11) is located at each transmitter channel's logic array interface. It compensates for the phase difference between the transmitter PCS clock and the local PLD clock.

In individual channel mode (for example, GIGE and Serial RapidIO), the low-speed parallel clock (or its divide-by-two version if the byte serializer is used) from the local clock divider block of each channel clocks the read port of its transmitter phase compensation FIFO buffer. This clock is also forwarded to the logic array on tx\_clkout port of its associated channel. If the tx\_coreclk port is not instantiated, the clock signal on the tx\_clkout port of Channel 0 is automatically fed back to clock the write port of the transmitter phase compensation FIFOs in all channels within the transceiver block. If the tx\_coreclk port is instantiated, the clock signal driven on the tx\_coreclk port clocks the write port of the transmitter phase compensation FIFO of its associated channel. You must ensure that the clock on the tx\_coreclk port is frequency-locked to the read clock of the transmitter phase compensation FIFO. For more information about using the PLD core clock (tx\_coreclk), refer to "PLD-Transceiver Interface Clocking" on page 1–50.

In bonded channel mode (for example, x4 PCI Express [PIPE]), the low-speed parallel clock from the central clock divider block is divided by two. This divide-by-two clock clocks the read port of the transmitter phase compensation FIFO. This clock is also forwarded to the logic array on the coreclkout port. If the tx\_coreclk port is not instantiated, the clock signal on the coreclkout port is automatically fed back to clock the write port of transmitter phase compensation FIFO buffers in all channels within the transceiver block. If the tx\_coreclk port is instantiated, the clock signal driven on the tx\_coreclk port clocks the write port of the transmitter phase compensation FIFO of its associated channel. You must ensure that the clock on the tx\_coreclk port is frequency locked to the read clock of the transmitter phase compensation FIFO. For more information about using the PLD core clock (tx\_coreclk), refer to "PLD-Transceiver Interface Clocking" on page 1–50.

Transmitter Channel datain[] dataout[] Transmitter Phase From PLD Compensation To Byte Serializer or PIPE **FIFO** or 8B/10B Interface Encoder rdclk tx\_coreclk CMU Local/Central Clock /2 Divider Block tx clkout coreclkout

Figure 1–11. Transmitter Phase Compensation FIFO

# Transmitter Phase Compensation FIFO Error Flag

The write port of the transmitter phase compensation FIFO can be clocked by either the CMU output clock or its divide-by-two version (tx\_clkout or coreclkout) or a PLD clock. The read port is always clocked by the CMU output clock or its divide-by-two version. In all configurations, the write clock and the read clock must have 0 PPM difference to avoid overrun/underflow of the phase compensation FIFO.

An optional debug\_tx\_phase\_comp\_fifo\_error port is available in all modes to indicate transmitter phase compensation FIFO overrun/underflow condition. This feature should be used for debug purpose only if link errors are observed.

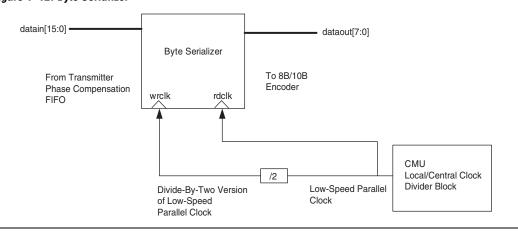

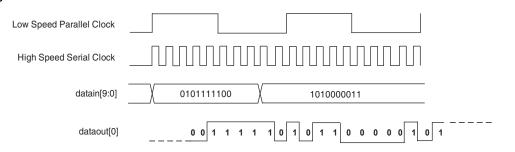

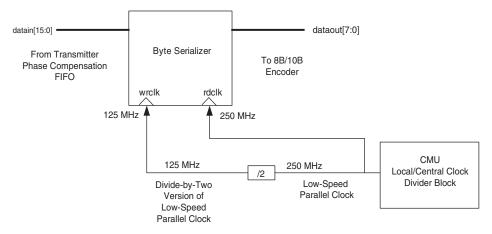

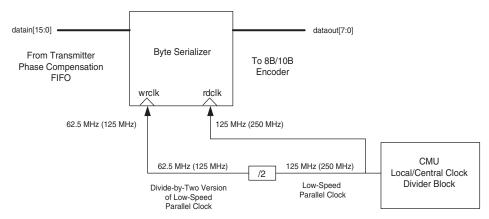

# Byte Serializer

In PCI Express (PIPE) and Serial RapidIO functional modes, the byte serializer (Figure 1–12) takes in 16-bit wide data from the transmitter phase compensation FIFO buffer and serializes it into an 8-bit wide data at twice the speed. This allows clocking the PLD-transceiver interface at half the speed as compared to the transmitter PCS logic. The byte serializer is bypassed in GIGE mode.

Figure 1-12. Byte Serializer

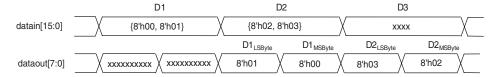

After serialization, the byte serializer transmits the least significant byte (LSByte) first and the most significant byte (MSByte) last.

Figure 1–13 shows byte serializer input and output. datain [15:0] is the input to the byte serializer from the transmitter phase compensation FIFO and dataout [7:0] is the output of the byte serializer.

Figure 1-13. Byte Serializer Operation

In Figure 1–13, the LSByte is transmitted before the MSByte from the transmitter byte serializer. For input data D1, the output data is  $D1_{LSByte}$  and then  $D1_{MSByte}$ .

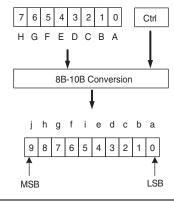

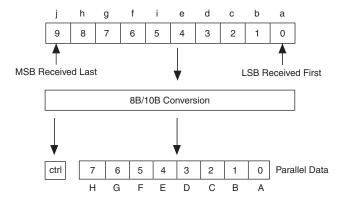

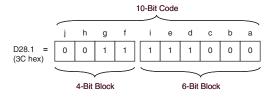

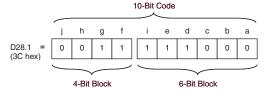

### 8B/10B Encoder

The 8B/10B encoder block takes in 8-bit data from the byte serializer (in PCI Express [PIPE] and Serial RapidIO modes) or transmitter phase compensation FIFO buffer (in GIGE mode). It generates a 10-bit code group with proper running disparity from the 8-bit character and a 1-bit control identifier (tx\_ctrlenable). The 10-bit code group is fed to the serializer. The 8B/10B encoder conforms to the IEEE 802.3 1998 edition standard.

Figure 1–14 shows the 8B/10B conversion format.

For additional information about 8B/10B encoding rules, refer to the *Specifications and Additional Information* chapter in volume 2 of the *Arria GX Device Handbook*.

Figure 1-14. 8B/10B Encoder

The 10-bit encoded data output from the 8B/10B encoder is fed to the serializer that transmits the data from LSB to MSB.

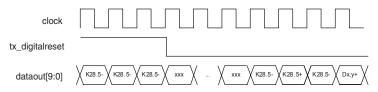

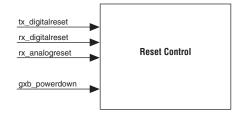

#### Reset Behavior

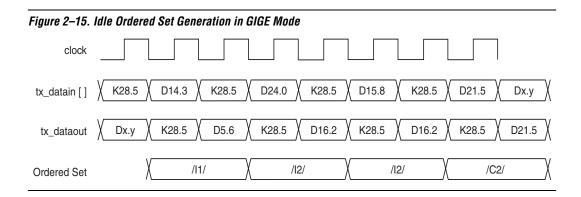

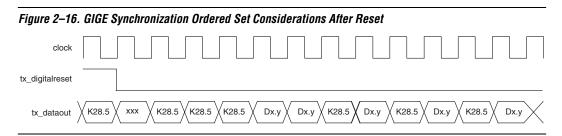

The transmitter digital reset (tx\_digitalreset) signal resets the 8B/10B encoder. During reset, the running disparity and data registers are cleared and the 8B/10B encoder outputs a K28.5 pattern from the RD-column continuously. Once out of reset, the 8B/10B encoder starts with a negative disparity (RD-) and transmits three K28.5 code groups for synchronizing before it starts encoding the input data or control character.

Figure 1–15 shows the 8B/10B encoder's reset behavior. When in reset (tx\_digitalreset is high), a K28.5- (K28.5 10-bit code group from the RD- column) is sent continuously until tx\_digitalreset is low. The transmitter channel pipelining causes some "don't cares (10'hxxx)" until the first of three K28.5 is sent. User data follows the third K28.5

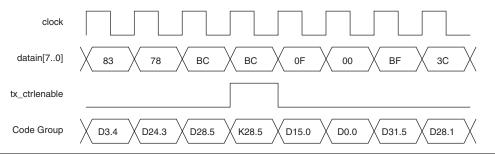

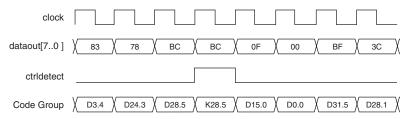

### Control Code Group Encoding

A control identifier (tx\_ctrlenable) input signal identifies if the 8-bit input character is to be encoded as a control word (Kx.y) or data word (Dx.y). When tx\_ctrlenable is low, the input character is encoded as data (Dx.y). When tx\_ctrlenable is high, the input character is encoded as a control word (Kx.y). The waveform in Figure 1–16 shows that the second 0xBC character is encoded as a control word (Kx.y). The rest of the characters are encoded as data (Dx.y).

The 8B/10B encoder does not check to see if the code group word entered is one of the 12 valid codes. If you enter an invalid control code, the resultant 10-bit code group may be encoded as an invalid code (does not map to a valid Dx.y or Kx.y code group), or unintended valid Dx.y code group, depending on the value entered.

### Transmitter Polarity Inversion

The positive and negative signals of a serial differential link might accidentally be swapped during board layout. Solutions such as a board re-spin or major updates to the PLD logic can prove expensive. The transmitter polarity inversion feature is provided to correct this situation.

An optional tx\_invpolarity port is available in all modes to dynamically enable the transmitter polarity inversion feature. A high on the tx\_invpolarity port inverts the polarity of every bit of the 10-bit input data word to the serializer in the transmitter data path. Since inverting the polarity of each bit has the same effect as swapping the positive and negative signals of the differential link, correct data is seen by the receiver. The tx\_invpolarity is a dynamic signal and may cause initial disparity errors at the receiver of an 8B/10B encoded link. The downstream system must be able to tolerate these disparity errors.

Figure 1–17 illustrates the transmitter polarity inversion feature.

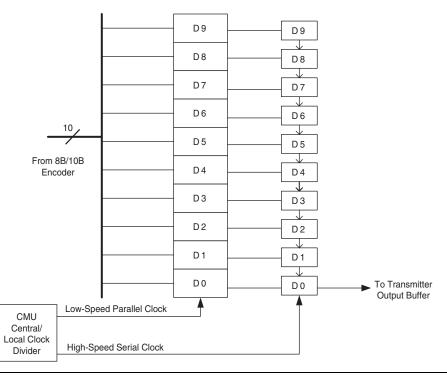

# Serializer

The serializer block clocks in 10-bit encoded data from the 8B/10B encoder using the low-speed parallel clock and clocks out serial data using the high-speed serial clock from the central or local clock divider blocks. The serializer feeds the data LSB to MSB to the transmitter output buffer.

Input to transmitter PMA

Output from transmitter PCS

Figure 1–18 shows the serializer block diagram.

Figure 1-18. Serializer

Figure 1–19 shows the serial bit order at the serializer output. In this example, 10'b17C data is serialized and transmitted from LSB to MSB.

## **Transmitter Buffer**

The transmitter buffer takes in serial data from the serializer and drives it on the tx\_dataout port of the associated transceiver channel.

Table 1–2 shows available transmitter buffer settings in each functional mode.

| Table 1–2. Transmitter Buffer Settings |                                            |                           |                                                      |                                              |              |

|----------------------------------------|--------------------------------------------|---------------------------|------------------------------------------------------|----------------------------------------------|--------------|

| Mode                                   | On-Chip<br>Termination with<br>Calibration | Supported I/O<br>Standard | Differential<br>Output Voltage<br>(V <sub>OD</sub> ) | Common Mode<br>Voltage<br>(V <sub>CM</sub> ) | Pre-Emphasis |

| PCI Express<br>(PIPE)                  | 100 Ω                                      | 1.2 V-PCML                | 800 mV                                               | 600 mV                                       | Enabled (1)  |

| GIGE                                   | 100 Ω                                      | 1.5 V-PCML                | 800 mV                                               | 600 mV                                       | Disabled     |

| Serial RapidIO                         | 100 Ω                                      | 1.5 V-PCML                | 800 mV                                               | 600 mV                                       | Disabled     |

#### Note to Table 1-2:

(1) In PCI Express (PIPE) mode, 49% pre-emphasis is used to meet the PCI Express de-emphasis specification.

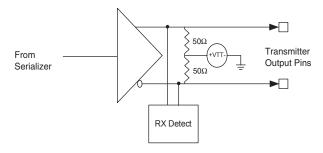

Figure 1–20 shows the transmitter buffer circuitry.

Figure 1-20. Transmitter Buffer

The transmitter buffer supports the Electrical Idle and Receiver Detect features in PCI Express (PIPE) mode.

Refer to the Transmitter Buffer section of the respective functional mode in the *Arria GX Transceiver Protocol Support and Additional Features* chapter in volume 2 of the *Arria GX Device Handbook* for more details about the supported features.

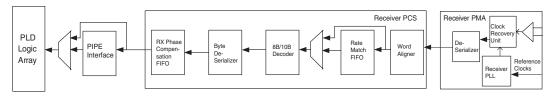

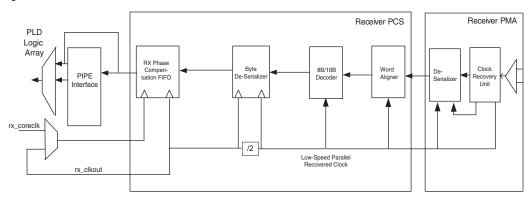

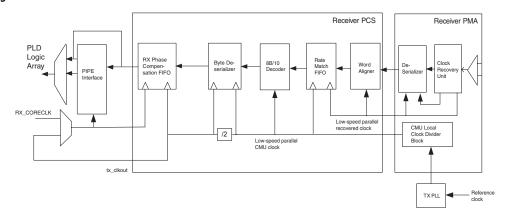

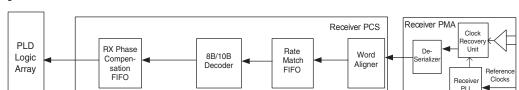

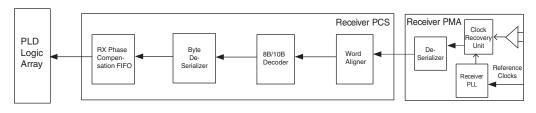

# Receiver Channel Architecture

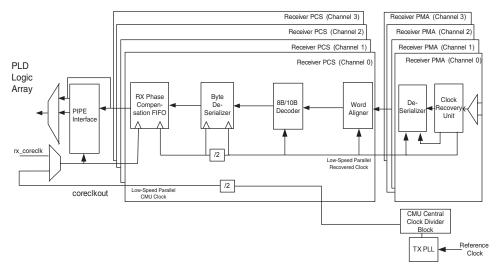

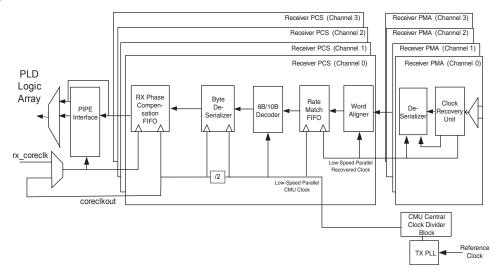

This section provides a brief description about sub-blocks within the receiver channel (Figure 1–21). The sub-blocks are described in order from the serial receiver input buffer to the receiver phase compensation FIFO buffer at the transceiver-PLD interface.

Figure 1-21. Receiver Channel Block Diagram

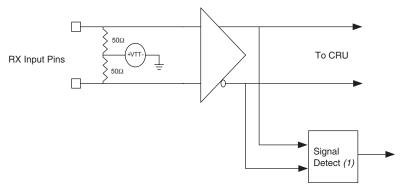

## **Receiver Buffer**

The receiver buffer receives serial data from the rx\_datain port and feeds it to the clock recovery unit (CRU).

Table 1–3 shows available receiver buffer settings in each functional mode.

| Table 1–3. Receiver Buffer Settings            |                                      |                                                                           |                                                 |          |  |

|------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------|----------|--|

| Mode                                           | On-Chip Termination with Calibration | Supported I/O<br>Standard                                                 | Common Mode<br>Voltage<br>(RX V <sub>CM</sub> ) | Coupling |  |

| PCI Express (PIPE),<br>GIGE,<br>Serial RapidIO | 100 Ω                                | 1.2 V-PCML,<br>1.5 V-PCML,<br>3.3 V-PCML,<br>Differential LVPECL,<br>LVDS | 850 mV                                          | AC       |  |

The receiver buffer also incorporates signal threshold detection circuitry only in PCI Express (PIPE) mode.

Refer to the Receiver Buffer section of the respective functional mode in the *Arria GX Transceiver Protocol Support and Additional Features* chapter in volume 2 of the *Arria GX Device Handbook* for more details about the supported features.

Figure 1–22 shows the receiver buffer circuitry.

Figure 1-22. Receiver Buffer

Note to Figure 1–22:

(1) The signal detect circuitry is available only in PCI Express (PIPE) mode.

#### **Receiver PLL**

Each transceiver channel has its own receiver PLL that is fed by an input reference clock. The reference clock frequency depends on the functional mode that the transceiver channel is configured for. The clock recovery unit (CRU) controls whether the receiver PLL locks to the input reference clock (lock-to-reference mode) or the incoming serial data (lock-to-data mode). Refer to "Clock Recovery Unit (CRU)" on page 1–27 for more details on lock-to-reference and lock-to-data modes. The receiver PLL, in conjunction with the clock recovery unit, generates two clocks: a high-speed serial clock that clocks the deserializer and a low-speed parallel clock that clocks the receiver's digital logic.

This section only discusses the receiver PLL operation in lock-to-reference mode. For lock-to-data mode, refer to "Clock Recovery Unit (CRU)" on page 1–27.

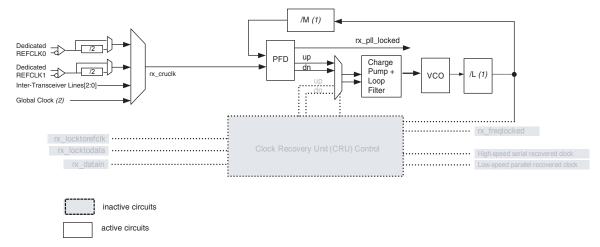

Figure 1–23 shows the block diagram of the receiver PLL in lock-to-reference mode.

Figure 1-23. Receiver PLL Block Diagram

#### *Notes to Figure 1–23:*

- You only need to select the protocol and the available input reference clock frequency in the Quartus II MegaWizard Plug-In Manager. Based on your selections, the Plug-In Manager automatically selects the necessary /M and /L dividers.

- (2) The global clock line must be driven from an input pin only.

The reference clock input to the receiver PLL can be derived from:

- One of the two available dedicated reference clock input pins (REFCLK0 or REFCLK1) of the associated transceiver block

- PLD clock network (must be driven directly from an input clock pin and cannot be driven by user logic or enhanced PLL)

- Inter-transceiver block lines driven by reference clock input pins of other transceiver blocks

Depending on the functional mode, the Quartus II software automatically selects the appropriate receiver PLL bandwidth.

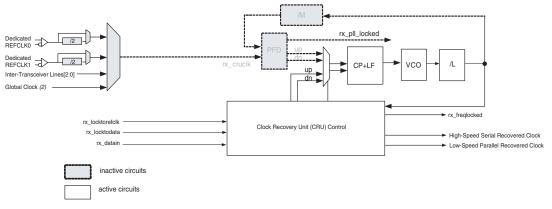

# **Clock Recovery Unit (CRU)**

The CRU (Figure 1–24) in each transceiver channel recovers the clock from the received serial data stream. You can set the CRU to lock to the received serial data phase and frequency (lock-to-data mode) to eliminate any clock-to-data skew or to keep the receiver PLL locked to the reference clock (lock-to-reference mode). The switch between lock-to-data and lock-to-reference modes can be done automatically or manually. The CRU

in conjunction with the receiver PLL generates two clocks: a high-speed serial recovered clock that feeds the deserializer and a low-speed parallel recovered clock that feeds the receiver's digital logic.

Figure 1-24. Clock Recovery Unit

#### Notes to Figure 1-24:

- (1) You only need to select the protocol and the available input reference clock frequency in the Quartus II MegaWizard Plug-In Manager. Based on your selections, the Plug-In Manager automatically selects the necessary /M and /L dividers.

- (2) The global clock line must be driven from an input pin only.

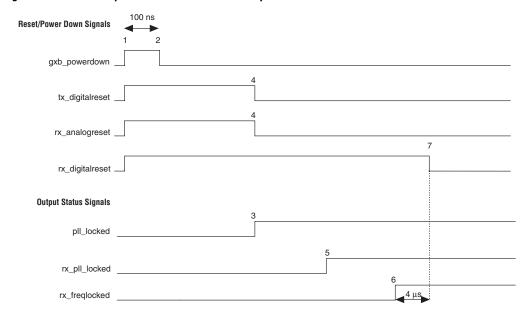

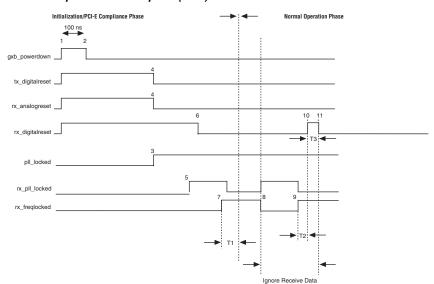

#### Automatic Lock Mode

After coming out of reset in automatic lock mode, the CRU initially sets the receiver PLL to lock to the input reference clock (lock-to-reference mode). After the receiver PLL locks to the input reference clock, the CRU automatically sets it to lock to the incoming serial data (lock-to-data mode) when the following two conditions are met:

- The receiver PLL output clock is within the configured PPM frequency threshold setting with respect to its reference clock (frequency locked)

- The reference clock and receiver PLL output clock are phase matched within approximately 0.08 UI (phase locked)

When the receiver PLL and CRU are in lock-to-reference mode, the PPM detector and the phase detector circuits monitor the relationship of the reference clock to the receiver PLL VCO output. If the frequency difference is within the configured PPM setting (as set in the MegaWizard Plug-In Manager) and the phase difference is within 0.08 UI, the CRU

switches to lock-to-data mode. The switch from lock-to-reference to lock-to-data mode is indicated by the assertion of the rx\_freqlocked signal.

In lock-to-data mode, the receiver PLL uses a phase detector to keep the recovered clock phase-matched to the data. If the PLL does not stay locked to data due to frequency drift or severe amplitude attenuation, the CRU switches back to lock-to-reference mode to lock the PLL to the reference clock. In automatic lock mode, the following condition forces the CRU to fall out of lock-to-data mode:

The CRU PLL is not within the configured PPM frequency threshold setting with respect to its reference clock

The switch from lock-to-data to lock-to-reference mode is indicated by the de-assertion of rx freqlocked signal.

When the CRU is in lock-to-data mode (rx\_freqlocked is asserted), it tries to phase-match the PLL with the incoming data. As a result, the phase of the PLL output clock may differ from the reference clock due to which rx\_pll\_locked signal might get de-asserted. You should ignore the rx\_pll\_locked signal when the rx\_freqlocked signal is asserted high.

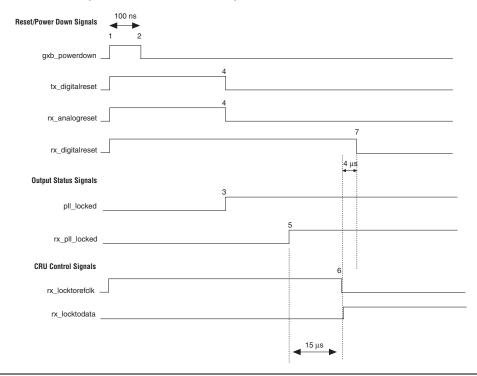

#### Manual Lock Mode

Two optional input pins (rx\_locktorefclk and rx\_locktodata) allow you to control whether the CRU PLL automatically or manually switches between lock-to-reference mode and lock-to-data mode. This enables you to bypass the default automatic switchover circuitry if either rx\_locktorefclk or rx\_locktodata is instantiated.

When the rx\_locktorefclk signal is asserted, the CRU forces the receiver PLL to lock to the reference clock. When the rx\_locktodata signal is asserted, the CRU forces the receiver PLL to lock to data. When both signals are asserted, the rx\_locktodata signal takes precedence over the rx\_locktorefclk signal, forcing the receiver PLL to lock to data.

The PPM threshold frequency detector and phase relationship detector reaction times may be too long for some applications. You can manually control the CRU to reduce PLL lock times using the rx\_locktorefclk and rx\_locktodata ports. Using the manual mode may reduce the time it takes for the CRU to switch from lock-to-reference mode to lock-to-data mode. You can assert the rx\_locktorefclk to initially

train the PLL to the reference clock. Once the receiver PLL locks to the reference clock, you can assert the rx\_locktodata signal to force the PLL to lock to the incoming data.

When the rx\_locktorefclk signal is asserted high, the rx\_freqlocked signal does not have any significance and is always driven low, indicating that the CRU is in lock-to-reference mode. When the rx\_locktodata signal is asserted high, the rx\_freqlocked signal is always driven high, indicating that the CRU is in lock-to-data mode. If both signals are de-asserted, the CRU is in automatic lock mode.

Table 1–4 shows a summary of the control signals.

| Table 1–4. CRU User Control Lock Signals |               |                         |  |  |

|------------------------------------------|---------------|-------------------------|--|--|

| rx_locktorefclk                          | rx_locktodata | CRU Mode                |  |  |

| 1                                        | 0             | Lock-to-reference clock |  |  |

| х                                        | 1             | Lock to data            |  |  |

| 0                                        | 0             | Automatic               |  |  |

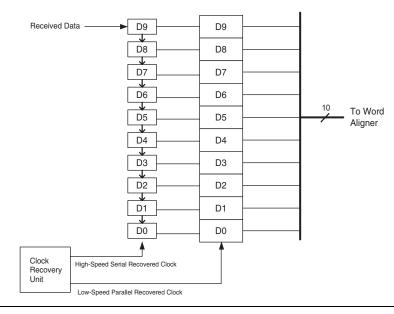

## Deserializer

The deserializer block clocks in serial input data from the receiver buffer using the high-speed serial recovered clock and deserializes it into 10-bit parallel data using the low-speed parallel recovered clock. It feeds the de-serialized 10-bit data to the word aligner as shown in Figure 1–25.

Figure 1-25. Deserializer

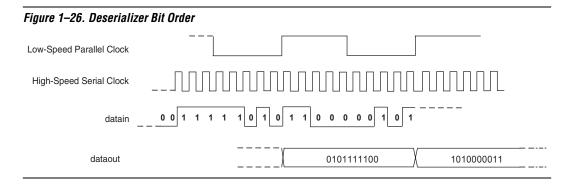

Figure 1–26 shows the serial bit order of the deserializer block input and the parallel data output of the deserializer block. A serial stream (0101111100) is de-serialized to a value 10'h17C. The serial data is assumed to be received LSB to MSB.

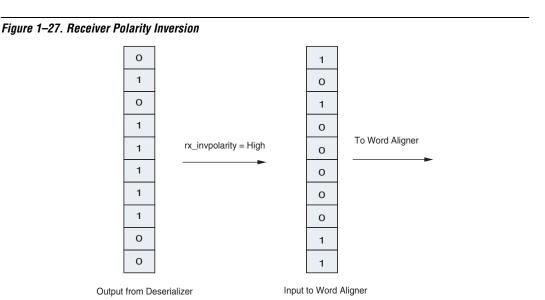

## Receiver Polarity Inversion

The positive and negative signals of a serial differential link might be accidentally swapped during board layout. Solutions such as a board re-spin or major updates to the PLD logic can prove expensive. The receiver polarity inversion feature is provided to correct this situation.

An optional rx\_invpolarity port is available in all modes to dynamically enable the receiver polarity inversion feature. A high on the rx\_invpolarity port inverts the polarity of every bit of the 10-bit input data word to the word aligner in the receiver data path. Since inverting the polarity of each bit has the same effect as swapping the positive and negative signals of the differential link, correct data is seen by the receiver. The rx\_invpolarity is a dynamic signal and may cause initial disparity errors in an 8B/10B encoded link. The downstream system must be able to tolerate these disparity errors.

The receiver polarity inversion feature is different from the PCI Express (PIPE) 8B/10B polarity inversion feature. The receiver polarity inversion feature inverts the polarity of the data bits at the input of the word aligner. The PCI Express (PIPE) 8B/10B polarity inversion feature inverts the polarity of the data bits at the input of the 8B/10B decoder and is available only in PCI Express (PIPE) mode. Enabling the generic receiver polarity inversion and the PCI Express (PIPE) 8B/10B polarity inversion simultaneously is not allowed in PCI Express (PIPE) mode.

Figure 1–27 illustrates the receiver polarity inversion feature.

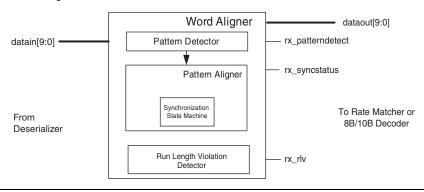

# **Word Aligner**

The word aligner clocks in 10-bit received data from the deserializer using the low-speed recovered clock. It restores the word boundary of the upstream transmitter based on the pre-defined word alignment character for the selected protocol. In addition to restoring the word boundary, the word aligner also implements a synchronization state machine in all functional modes to achieve lane synchronization.

The word aligner consists of three sub-modules:

- Pattern detector module

- Pattern aligner module

- Run length violation detector module

Figure 1–28 shows the block diagram for the word aligner block.

Figure 1-28. Word Aligner

#### Pattern Detector Module

The pattern detector looks for the configured word alignment pattern in the data clocked into the word aligner. When the pattern detector detects the word alignment pattern for the first time, it asserts the rx\_patterndetect signal. The pattern aligner aligns the word boundary to the received word alignment pattern. Any subsequent word alignment pattern found in the same word boundary causes the rx\_patterndetect signal to assert for one parallel clock cycle. The rx\_patterndetect signal is not asserted if the word alignment pattern is found across the current word boundary.

All three supported functional modes, PCI Express (PIPE), GIGE, and Serial RapidIO, specify K28.5 (10'b0101111100 or 10'b1010000011) as the synchronization code group. The Quartus II software automatically programs both disparities of K28.5 control word as the word alignment pattern in all three modes.

## Pattern Aligner Module

The pattern aligner module, in conjunction with the pattern detector, aligns the received data to the pre-defined word alignment pattern. The pattern aligner incorporates an automatic synchronization state machine in all supported functional modes.

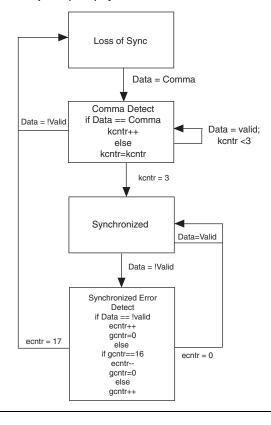

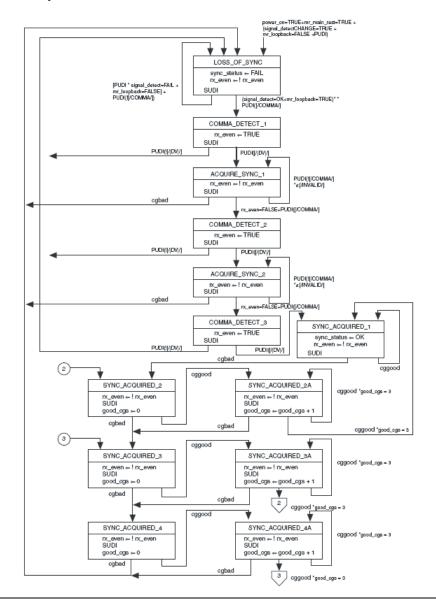

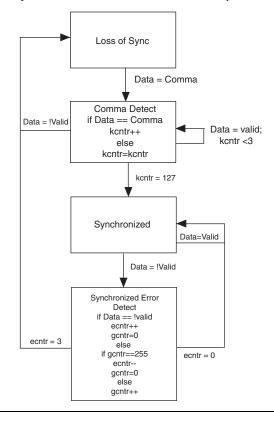

### **Automatic Synchronization State Machine**

The synchronization state machine offers automatic detection of a pre-defined number of valid alignment patterns to indicate lane synchronization and detection of code group errors for falling out of synchronization. The synchronization state machine indicates lane synchronization status on the rx\_syncstatus port. A high signal on the rx\_syncstatus port indicates that the lane synchronization has been achieved and a low signal indicates that the lane is not synchronized. In synchronized state (as indicated by rx\_syncstatus asserted high), the pattern aligner does not re-align the word boundary if the pattern detector detects the word alignment pattern in the incoming data. It re-aligns the word boundary only when the synchronization state machine detects loss of synchronization state (as indicated by rx\_syncstatus de-asserted low).

The Quartus II software automatically configures the synchronization state machine parameters; for example, number of valid synchronization characters received and number of invalid code groups received to fall out of synchronization. It selects these parameters as specified by each protocol standard (functional mode).

### Run Length Violation

The programmable run-length violation circuit resides in the word aligner block and detects consecutive 1s or 0s in the data. If the data stream exceeds the preset maximum number of consecutive 1s or 0s, the violation is signified by the assertion of the rx rlv signal.

The rx\_rlv signal is not synchronized to the parallel data and appears in the logic array earlier than the run-length violation data. To ensure that the PLD can latch this signal in systems where there are frequency variations between the recovered clock and the PLD logic array clock, the rx\_rlv signal is asserted for a minimum of two clock cycles. The rx\_rlv signal may be asserted longer, depending on the run-length of the received data.

In all supported functional modes, you can set the run length violation circuitry to detect up to 160 consecutive 1s or 0s. The run length settings are available in increments of five.

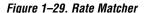

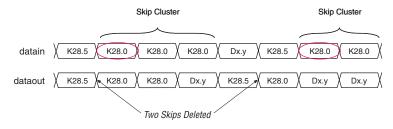

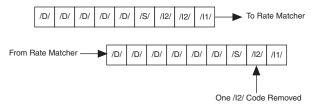

### **Rate Matcher**

In asynchronous systems, the upstream transmitter and the local receiver may be clocked with independent reference clock sources. Frequency differences in the order of a few hundred parts per million (PPM) can potentially corrupt the data at the receiver. The rate matcher compensates for small clock frequency differences between the upstream transmitter and the local receiver clocks by inserting or removing skip characters or ordered-sets from the inter-packet gap (IPG) or idle streams. It inserts a skip character or ordered-set if the local receiver is running a faster clock than the upstream transmitter. It deletes a skip character or ordered-set if the local receiver is running a slower clock than the upstream transmitter. The rate matcher is available only in PCI Express (PIPE) and GIGE functional modes. The Quartus II software automatically configures the appropriate skip character or ordered-set as specified in the Gigabit Ethernet and PCI Express Base Specification depending on the selected functional mode.

The rate matcher consists of a 20-word-deep FIFO buffer and necessary logic to detect and perform the insertion and deletion functions. The write port of the rate matcher FIFO is clocked by the low-speed parallel recovered clock. The read port is clocked by the low-speed parallel clock from the CMU central or local clock divider block (Figure 1–29).

### 8B/10B Decoder

The 8B/10B decoder takes in 10-bit data from the rate matcher and decodes it into 8-bit data + 1-bit control identifier, thereby restoring the original transmitted data at the receiver. The decoded data is fed to the byte deserializer (in PCI Express [PIPE] and Serial RapidIO modes) or the receiver phase compensation FIFO buffer (in GIGE mode). The 8B/10B decoder conforms to IEEE 802.3 1998 edition standards.

Figure 1–30 shows a 10-bit code group decoded to an 8-bit data and a 1-bit control indicator.

Figure 1-30. 10-Bit to 8-Bit Conversion

### Control Code Group Detection

The 8B/10B decoder differentiates between data and control codes through the rx\_ctrldetect port. If the received 10-bit code group is a control code group (Kx.y), the rx\_ctrldetect signal is driven high, and if it is a data code group (Dx.y), the rx\_ctrldetect signal is driven low.

Figure 1–31 shows an example waveform demonstrating the receipt of a K28.5 code group (BC + ctrl). The rx\_ctrldetect=1 'b1 is aligned with 8'hbc, indicating that it is a control code group. The rest of the codes received are Dx.y code groups.

Figure 1-31. Control Code Group Detection

### Code Group Error Detection

If the received 10-bit code group is not a part of valid Dx.y or Kx.y code groups, the 8B/10B decoder block asserts an error flag on rx\_errdetect port. The error flag signal (rx\_errdetect) has the same data path delay from the 8B/10B decoder to the PLD-transceiver interface as the invalid code group.

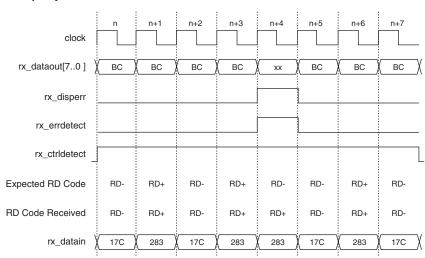

### Disparity Error Detection

If the received 10-bit code group is detected with incorrect running disparity, the 8B/10B decoder block asserts an error flag on rx\_disperr and rx errdetect port.

Refer to the *Specifications & Additional Information* chapter in volume 2 of the *Arria GX Device Handbook* for information about the disparity calculation.

If negative disparity is calculated for the last 10-bit code group, a neutral or positive disparity 10-bit code group is expected. If the 8B/10B decoder does not receive a neutral or positive disparity 10-bit code group, the rx\_disperr signal goes high, indicating that the code group received has a disparity error. Similarly, if a neutral or negative disparity is expected and a 10-bit code group with positive disparity is received, the rx\_disperr signal goes high.

The detection of the disparity error might be delayed, depending on the data that follows the actual disparity error. The 8B/10B control codes terminate propagation of the disparity error. Any disparity errors propagated stop at the control code group, terminating that disparity error.

Figure 1–32 shows a case where the disparity is violated. A K28.5 code group has an 8-bit value of 8'hbc and a 10-bit value that depends on the disparity calculation at the point of the generation of the K28.5 code group. The 10-bit value is 10'b0011111010 (10'h17c) for RD– or

10'b1100000101 (10'h283) for RD+. If the running disparity at time n - 1 is negative, the expected code group at time must be from the RD– column. A K28.5 does not have a balanced 10-bit code group (equal number of 1s and 0s), so the expected RD code group must toggle back and forth between RD– and RD+. At time n + 3, the 8B/10B decoder received a RD+ K28.5 code group (10'h283), which makes the current running disparity negative. At time n + 4, because the current disparity is negative, a K28.5 from the RD– column is expected, but a K28.5 code group from the RD+ is received instead. This prompts  $rx\_disperr$  to go high during time n + 4 to indicate that this particular K28.5 code group had a disparity error. The current running disparity at the end of time n + 4 is negative because a K28.5 from the RD+ column was received. Based on the current running disparity at the end of time n + 5, a positive disparity K28.5 code group (from the RD–) column is expected at time n + 5.

Figure 1-32. Disparity Error Detection

### Reset Condition

The reset for the 8B/10B decoder block is derived from the receiver digital reset (rx\_digitalreset). When rx\_digitalreset is asserted, the 8B/10B decoder block resets. In reset, the disparity registers are cleared and the outputs of the 8B/10B decoder block are driven low. After reset, the 8B/10B decoder starts with unknown disparity, depending on the disparity of the data it receives. The decoder calculates the initial running disparity based on the first valid code group received.

The receiver block must be word aligned after reset before the 8B/10B decoder can decode valid data or control codes. If word alignment has not been achieved, the data from the 8B/10B decoder should be discarded and considered invalid.

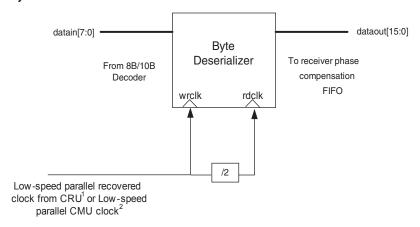

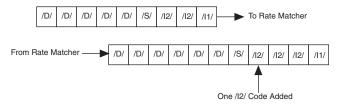

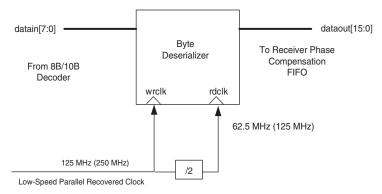

### Byte Deserializer

In PCI Express (PIPE) and Serial RapidIO functional modes, the byte deserializer (Figure 1–33) takes in 8-bit wide data from the 8B/10B decoder and deserializes it into a 16-bit wide data at half the speed. This allows clocking the PLD-transceiver interface at half the speed as compared to the receiver PCS logic. The byte deserializer is bypassed in GIGE mode.

Figure 1-33. Byte Deserializer

#### *Notes to Figure 1–33:*

- (1) Write port is clocked by low-speed parallel recovered clock if rate matcher is not used.

- (2) Write port is clocked by low-speed parallel CMU clock if rate matcher is used.

If the byte deserializer is used, the byte ordering at the receiver output might be different than what was transmitted. Figure 1–34 shows the 16-bit transmitted data pattern with A at the lower byte, followed by B at the upper byte. C and D follow in the next lower and upper bytes, respectively. At the byte deserializer, byte A arrives when it is stuffing the upper byte instead of stuffing the lower byte. This is a non-deterministic swap because it depends on PLL lock times and link delay. You must implement byte-ordering logic in the PLD to correct this situation.

Figure 1–34. Intended Transmitted Pattern and Incorrect Byte Position at Receiver After Byte Serializer

| Χ | В | D |  |

|---|---|---|--|

| Χ | Α | С |  |

Intended Transmitted

Pattern

| Α | С | Х |

|---|---|---|

| Х | В | D |

Incorrect Byte Position at Receiver

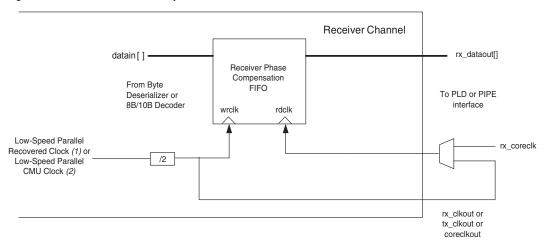

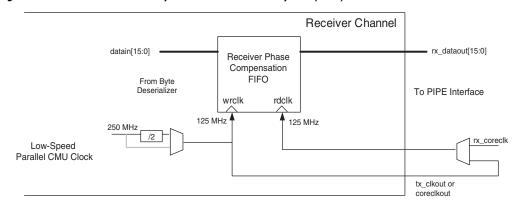

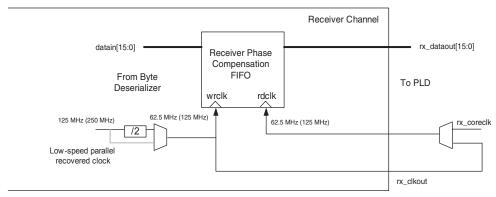

### **Receiver Phase Compensation FIFO buffer**

A receiver phase compensation FIFO buffer (Figure 1–35) is located at each receiver channel's logic array interface. It compensates for the phase difference between the receiver PCS clock and the local PLD clock.

In individual channel mode with rate matcher (PCI Express [PIPE] ×1 and GIGE), the low-speed clock output from the local clock divider block of each channel or its divide-by-two version clocks the write port of its receiver phase compensation FIFO buffer. This clock is also forwarded to the logic array (tx\_clkout). In individual channel mode without rate matcher (Serial RapidIO), the low-speed parallel recovered clock from the CRU is divided by two. This divide-by-two clock clocks the write port of its receiver phase compensation FIFO buffer. This clock is also forwarded to the logic array (rx\_clkout). If the rx\_coreclk port is instantiated, the clock signal on the rx\_coreclk port clocks the read port of the FIFO. If the rx\_coreclk port is not instantiated, the clock signal on tx\_clkout (if rate matcher is used) or rx\_clkout (if rate matcher is not used) port is automatically fed back to clock the read port of the FIFO.

In bonded channel mode (x4 PCI Express [PIPE]), the low-speed clock output from the central clock divider block is divided by two. This divide-by-two clock clocks the write port of the receiver phase compensation FIFO buffers in all channels. This clock is also forwarded to the logic array (coreclkout). If the rx\_coreclk port is instantiated, the clock signal on the rx\_coreclk port clocks the read port of the FIFO. If the rx\_coreclk port is not instantiated, the clock signal on the coreclkout port is automatically fed back to clock the read port of the FIFO in all channels within the transceiver block.

Figure 1–35. Receiver Phase Compensation FIFO Buffer

Notes to Figure 1-35:

- (1) Write port is clocked by low-speed parallel recovered clock when rate matcher is not used.

- (2) Write port is clocked by low-speed parallel CMU clock when rate matcher is used.

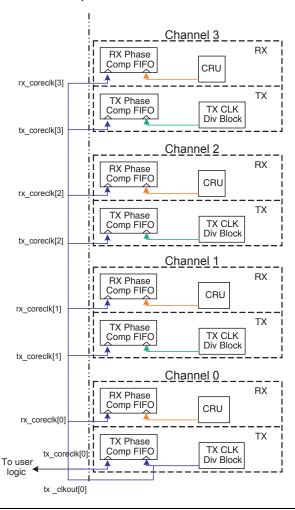

# Transceiver Channel Clock Distribution

This section describes clock distribution within the transceiver channel for all supported functional modes. Clock distribution can be classified into two categories:

- Individual-channel mode clocking—GIGE, Serial RapidIO, and PCI Express [PIPE] ×1 functional modes fall in this category

- Bonded-channel mode clocking—PCI Express (PIPE) ×4 functional mode falls in this category

### **Individual-Channel Mode Clocking**

In GIGE, Serial RapidIO, and PCI Express (PIPE) ×1 functional modes, each channel within the transceiver block forms an independent link. The blocks in the transmitter and receiver data paths of each channel are clocked independently and do not share any control signals. The transmitter channel-to-channel skew in individual channel modes could be relatively higher compared to bonded-channel mode.

### Individual-Channel Mode Transmitter Clock Distribution

Figure 1–36 shows clock distribution within a transmitter channel when configured in one of the individual-channel modes.

Figure 1–36. Individual-Channel Mode Transmitter Clock Distribution

The transmitter PLL multiplies the input reference clock to generate a high-speed serial clock at a frequency that is half the data rate of the configured functional mode. This high-speed serial clock is fed to the local clock divider block in each channel within the transceiver block. Depending on the configured functional mode, the local clock divider block divides the high-speed serial clock to generate the low-speed parallel clock that clocks the transmitter PCS logic in the associated channel.

Table 1–5 shows high-speed serial clock frequencies, low-speed parallel clock frequencies, and PLD-transceiver interface frequencies for individual-channel functional modes.

| Table 1–5. CMU Output Clock Frequencies |                                            |                                                |                                                 |  |  |

|-----------------------------------------|--------------------------------------------|------------------------------------------------|-------------------------------------------------|--|--|

| Functional Mode                         | High-Speed Serial Clock<br>Frequency (MHz) | Low-Speed Parallel<br>Clock Frequency<br>(MHz) | PLD-Transceiver<br>Interface Frequency<br>(MHz) |  |  |

| PCI Express (PIPE) x1 (2.5 Gbps)        | 1250                                       | 250                                            | 125                                             |  |  |

| GIGE (1.25 Gbps)                        | 625                                        | 125                                            | 125                                             |  |  |

| Serial RapidIO (1.25 Gbps)              | 625                                        | 125                                            | 62.5                                            |  |  |

| Serial RapidIO (2.5 Gbps)               | 1250                                       | 250                                            | 125                                             |  |  |

In functional modes that use the byte serializer (PCI Express [PIPE] x1 and Serial RapidIO), the low-speed parallel clock is divided by two before being driven on the tx clkout port. In GIGE mode that does not use the byte serializer, the low-speed parallel clock is directly driven on the tx clkout port. If the tx coreclk port is not instantiated, the Quartus II software automatically clocks the write port of the transmitter phase compensation FIFO in each channel with the tx clkout signal of channel 0 (tx clkout [0]) of that transceiver block. In PCI Express (PIPE) x1 mode, the tx\_clkout signal also clocks each channel's PCI Express (PIPE) interface logic. The read port of the transmitter phase compensation FIFO is clocked by the low-speed parallel clock output (or its divide-by-two version if byte serializer is used) of the channel's local clock divider block. The read port of the byte deserializer block (if used) is clocked by the low-speed parallel clock and the write port is clocked by its divide-by-two version. The 8B/10B encoder is clocked by the low-speed parallel clock. The 10-bit input data to the serializer block is clocked by the low-speed parallel clock and the serialized data is clocked out by the high-speed serial clock.

### Individual-Channel Mode Receiver Clock Distribution

The clock distribution within a receiver channel varies depending on whether rate matcher is used or not. GIGE and functional modes have a rate matcher in the receiver data path to compensate for the frequency difference between the upstream transmitter and local receiver clock. Serial RapidIO and Low-Latency (Synchronous) PCI Express (PIPE) ×1 modes do not have a rate matcher in the receiver data path.

#### Receiver Clock Distribution Without the Rate Matcher

Figure 1–37 shows clock distribution within a receiver channel when configured in an individual-channel mode without a rate matcher (Serial RapidIO and Low-Latency [Synchronous] PCI Express [PIPE] ×1 modes).