# The L3 Data Buffer on the Daughterboards 5 July, 2002

#### 1) Introduction

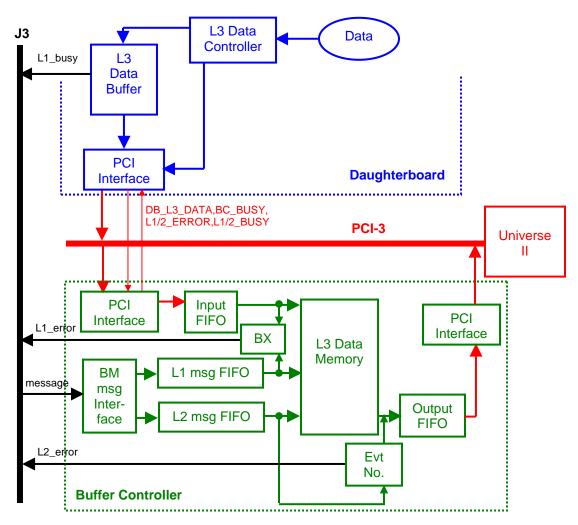

The current design of the Buffer Controller (BC) makes several requirements on the daughterboards (DB) that supply it with data to be stored in its memory for every L1 Accept. A simplified block diagram of the DB – BC communications is given in Fig. 1.

Figure 1: Block diagram of DB - BC communications.

### 2) Buffer Implementation

The life of the BC is made easier if the L3 Data Buffers on the DBs are FIFOs. This allows PCI block reads to always be performed from the same address.

#### 3) Size of the Buffer

The required depth of the L3 Data Buffers on the various DBs is set by PCI-3 occupancy issues. This is discussed in detail in *PCI Bus-3 Use and Data Buffering*<sup>1</sup>. To summarize, the minimum depth in 32-bit words required for the L3 Data Buffers on the different DBs is:

**FRC** 154 words **STC** 9216 words **TFC** 6267 words

#### 4) Format of the Data

Data in the L3 Data Buffers should be stored in a format as close as possible to that expected by the VBD when it reads out the BC Output FIFO. This way, the BC has to do as little reformatting as possible. There are three requirements imposed on the DB L3 data by the BC. The BC performs checks on all three of these and generates errors if any of them fail.

- 1) BX as received by the DB should be stored in the lowest 8 bits of the first word in the DB's L3 data.

- 2) The total number of 32-bit words in the DB's L3 data, including the final checksum, should be included as the next-to-last word in the L3 data.

- 3) A checksum (vertical parity) should be included as the last word in the DB's L3 data.

The format of the L3 data block from the DBs is shown in Table 1

| 31                                    | 24  | 23  | 16  | 15       | 8      | 7 | 0  |

|---------------------------------------|-----|-----|-----|----------|--------|---|----|

| unus                                  | sed | uni | sed | reserved | for BC | H | BX |

| Data                                  |     |     |     |          |        |   |    |

| ••••                                  |     |     |     |          |        |   |    |

| Data                                  |     |     |     |          |        |   |    |

| Total Word Count (including checksum) |     |     |     |          |        |   |    |

| 32-bit checksum (vertical parity)     |     |     |     |          |        |   |    |

**Table 1:** Possible format for L3 data from DBs.

## 5) Transferring Data to the Buffer Controller

Transfer of data from the L3 Data Buffer on the DB to the BC will be done as a PCI block transfer with the BC acting as Master and the DB as Target. (This simplifies the DB PCI-3 interface.) Since the BC knows neither when the L3 Data Buffer is ready with an event's worth of data to transfer nor how much data is present, a standard PCI block transfer cannot be done. Two additional features are necessary:

- 1) The DB must signal the BC that the L3 Data Buffer is ready. This handshaking is done using the *SPARE0* (=DB\_L3\_DATA) *SPARE1* (=BC\_BUSY) lines that are present in the *Updated Motherboard Spec*<sup>2</sup>.

- 2) The DB must signal that it is transferring the last data word in the block to the BC. This is accomplished by having the DB PCI interface use *target-disconnect* (without data) mode.

#### 5.1 Advertising Data Ready

The details of the L3 data transfer between the DB and the BC are driven by the fact that the BC must act as the master in this transaction (the DB is the target), however, the BC knows neither when the DB's L3 data is ready nor how many words are contained in that data. This requires some handshaking between the DB and the BC involving two special purpose lines (*DB\_L3\_DATA* and *BC\_BUSY*, corresponding to *SPARE0* and *SPARE1* respectively on the motherboard – see the *Buffer Controller – Logic Daughterboard Communications* document<sup>3</sup>) as well as PCI signals involved in *target-disconnect-without-data* block transfers.

The steps in the handshaking are the following.

- 1) The DB indicates to the BC that it has L3 data to be transferred by asserting *DB\_L3\_DATA*. This can be done as soon as data appears in the DB's L3 FIFO or can wait until all data is present. (In the FRC *DB\_L3\_DATA* is raised as soon as data enters the FIFO).

- 2) When the BC sees *DB\_L3\_DATA*, it begins the process of requesting a PCI block transfer, which also requires information from the BM. (See the Altera Megacore manual for PCI details). The BC also asserts *BC\_BUSY* as soon as it issues the request.

- 3) The DB signals the BC PCI interface that it is ready to transmit data as soon as all of its L3 data is stored in its L3 FIFO. This is done following standard PCI block transfer protocol. For example, in the FRC, *lt\_rdyn* is asserted when the last L3 data word is loaded into the FIFO.

- 4) The BC begins the block transfer.

- 5) The block transfer is terminated by the DB after its last L3 word using the *target-disconnect-without-data* protocol. *DB\_L3\_DATA* should be deasserted at this time.

## References

<sup>&</sup>lt;sup>1</sup> PCI Bus-3 Use and Data Buffering <a href="http://www.nevis.columbia.edu/~evans/stt/sb">http://www.nevis.columbia.edu/~evans/stt/sb</a> 0700/PCI-3.pdf

<sup>&</sup>lt;sup>2</sup> E. Hazen and S. Wu, *Motherboard Electrical Specification Update* (7 July, 2000)

<sup>&</sup>lt;sup>3</sup> Buffer Controller – Logic Daughterboard Communications http://www.nevis.columbia.edu/~evans/stt/sb\_0700/BC\_DB.pdf